# Design of Xilinx Based Telemetry System Using Verilog

N. P. Lavanya Kumari<sup>1</sup>, A. Sarvani<sup>2</sup>, K. S. S. Soujanya Kumari<sup>3</sup>, L. Y. Swathi<sup>4</sup>, M. Purnachandra Rao<sup>5</sup>

<sup>1</sup>Assistant.Professor (C), Department of Systems Design, Andhra University, Visakhapatnam, Andhra Pradesh, India <sup>2, 3,4</sup>Research Scholar, Department of Systems Design, Andhra University, Visakhapatnam, Andhra Pradesh, India <sup>5</sup>Guide & Head of Department, Department of Systems Design, Andhra University, Visakhapatnam, Andhra Pradesh, India

Abstract: Telemetry is a technology that allows the remote measurement and reporting of information of interest to the system designer or operator. The transmission media may be air and space for satellite applications and copper wire and fiber cables for static ground environments like power generation plants. A sure and effective telemetry link system plays a vital role in controlling and commanding the aircraft or satellite. The telemetry, tracking and command (TT&C) system of a spacecraft provides the most vital telecommunication link between a satellite and ground station. The TT&C systems provide the uplink for command and downlink for monitoring the various health parameters through telemetry and much needed tracking information for the satellite for monitoring its position in the orbit .The link is provided using a ground station and onboard telecomm and & tracking data receiving system onboard decoder and telemetry transmitter. The TT&C link of a satellite is of prime importance, right from the time of its launch to the end of the mission. In this paper, telemetry system is developed to communicate data that identified in the objects characterization or parameters which give a clear idea to analyze the moving objects in real time and space which is an important characterization in day to day life. The aim of the paper is to design a telemetry system in VERILOG and successfully simulated it through XILINX. By this, an effective link using digital techniques is developed. The digital techniques used in design makes the FSK modulator and demodulator sections to be flexible in modifying the frequencies and other parameters. By the features of XILINX the code was generated successfully and simulation results can be dumped into an FPGA. Thus results a practical telemetry system. By using more advanced techniques we can design a telemetry system which can be more reliable and accurate in transmission.

Keywords: Telemetry, XILINX, VERILOG, FPGA

#### **1. Introduction**

Telemetry is defined as the sensing and measuring of information at some remote Location and then transmitting that information to a central or host location. There, it can be monitored and used to control a process at the remote site. The word is derived from the Greek root tele=remote, metron=measure. Telemetry is the process by which an object's characteristics are measured (such as velocity of an aircraft), and the results transmitted to a distant station where they are displayed, recorded, and analyzed. The transmission media may be air and space for satellite applications, or copper wire and fiber cable for static ground environments like power generating plants. The purpose of a telemetry system is to collect data at a place that is remote or inconvenient and to relay the data to a point where the data may be evaluated. The basic concept of telemetry has been in existence for centuries. Various mediums or methods of transmitting data from one site to another have been used. Data radio provides a wireless method for transmitting the information. Telemetry using radio waves or wireless offers several distinct advantages over other transmission methods. Some of these advantages are:

- 1. No transmission lines to be cut or broken.

- 2. Faster response time

- 3. Lower cost compared to leased lines

- 4. Ease of use in remote areas where it is not practical or possible to use wire or coaxial cables

- 5. Easy relocation

- 6. Functional over a wide range of operating conditions

Properly designed radio links can provide low cost, effective and flexible data gathering systems that operate for many years with very little maintenance. The Telemetry, Tracking and Command (TT&C) Systems of a spacecraft provides the most vital telecommunication link between a satellite and ground station. The TT&C systems provide the uplink for command, downlink for monitoring the various health parameters through telemetry and much needed tracking information for the satellite for monitoring its position in orbit. The link is provided using a ground station and onboard tele-command & tracking data receiving systems, onboard decoder and telemetry transmitter. The TT&C link of a satellite is of prime importance, right from the time of its launch to the end of the mission.

#### 2. Design Overview

Today's telemetry systems are built from commercial-offthe-shelf (COTS) products. But while they all have many common elements, they are each uniquely configured to meet specific application requirements. A telemetry system is often viewed as two components, the Airborne System and the Ground System. In actuality, either or both may be in the air or on the ground.

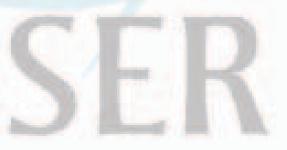

Figure 1.1. Telemetry transmitter section

Data acquisition begins when sensors (aka, transducers) measure the amount of a physical attribute and transform the measurement to an engineering unit value. Some sensors produce a voltage directly (thermocouples for temperature or piezoelectric strain gages for acceleration), while others require excitation (resistive strain gages, potentiometers for rotation, etc.). Sensors attached to signal conditioners provide power for the sensors to operate or modify signals for compatibility with the next stage of acquisition. Since maintaining a separate path for each source is cumbersome and costly, a multiplexer (historically known as a commutator) is employed. It serially measures each of the analog voltages and outputs a single stream of pulses, each with a voltage relative to the respective measured channel. The rigorous merging of data into a single stream is called Time Division Multiplexing or TDM.

Figure 1.2: Time division multiplexing

The scheme where the pulse height of the TDM stream is proportional to the measured value is called Pulse Amplitude Modulation (PAM). A unique set of synchronization pulses is added to identify the original measurands and their value. PAM has many limitations, including accuracy, constraints on the number of measurands supported, and the poor ability to integrate digital data.

Pulse Code Modulation (PCM) is today's preferred telemetry format for the same reasons that PAM is inadequate. Accuracy is high, with resolution limited only by the analog to digital converter (ADC), and thousands of measurands can be acquired along with digital data from multiple sources, including the contents of the computer's memory and data buses. In a PCM-based system, the original PAM multiplexer's analog output is digitized to a parallel format. The Output Formatter along with synchronization data for measurand identification merges this, plus other sources of digital data. The Output Formatter serializes the composite parallel data stream to a binary string of pulses (1's and 0's) for transmission on copper wire, fiber cable, or "the ether." All components from after the sensor to the formatter comprise the encoder (see figure below}. Other, often remote encoders are used to multiplex additional sensor data into the main encoder's output. Not only does this expand the number of measurands to

thousands per stream, but it also eliminates the weight of cables required for each sensor. The output of the main encoder is filtered and transmitted via radio transmitter and antenna, coax cable, telephone line, tape recorder, etc. Filtering rounds or smoothes the square data pulses to reduce frequency content and thus the required transmitter bandwidth. At the Ground Station, the received data stream is amplified. Since the transmission path often distorts the already rounded signal, a bit synchronizer reconstructs it to the original serial square wave train. Then, a decommutator or decom (similar to that found in L-3' Visual Test System or System 550) recognizes the synchronization pattern and returns the serial digital stream to parallel data. Decom also separates the PCM stream into its original measurands (also known as prime parameters) and data.

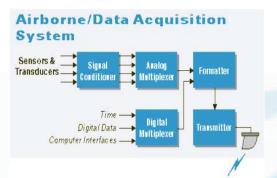

Figure 1.3: Telemetry receiver sections

The computer (in the Visual Test System) or the telemetry front end (System 550) selects prime parameters for realtime processing; archiving to disk or tape; display; output to strip chart recorders and annunciates; or distribution to other computing resources according to the test plan.

L-3 Telemetry-West and its sister divisions manufacture virtually the entire telemetry system — from signal conditioners to antennas for the Airborne System and from antennas to telemetry receivers for the Ground System. The following table breaks down which L-3 divisions provide what for today's telemetry system requirements. Just remember that when you need to put everything together, L-3 Telemetry-West will help specify, integrate, and install all L-3 and third-party components for a total telemetry solution.

## 3. Design Techniques

To design the code for telemetry systems Manchester coding technique and for modulation BFSK modulation scheme is used.

## 3.1 Manchester Encoding

Manchester encoding has gained wide acceptance as the modulation scheme for low-cost radiofrequency transmission of digital data. This form of binary phase-shift keying is a simple method for encoding digital serial data of arbitrary bit patterns without any long strings of continuous

## International Journal of Scientific Engineering and Research (IJSER)

www.ijser.in ISSN (Online): 2347-3878 Volume 2 Issue 3, March 2014

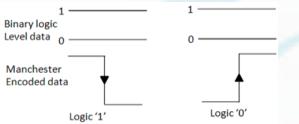

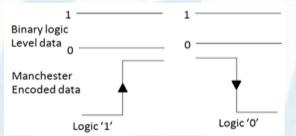

zeros or ones, and having the encoding clock rate embedded within the transmitted data. The encoding of digital data in Manchester format defines states of "1" and "0" to be transitions rather than static values. There are two possible definitions (as shown in Figures 3.1 and 3.2) that have alternate assignments of the logic levels to the two possible transitions of rising and falling edges.

Figure 3.1: Defining logical binary data as edge transitions

Figure 3.2: Equally valid alternate definitions of binary data as edge transitions

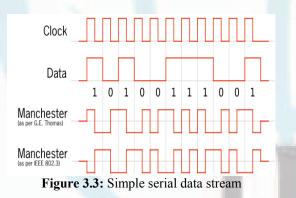

Thus, each Manchester data encoding of a logic level bit requires two chips. A simple serial data stream is shown in Figure.3.3.

#### 3.2. Digital BFSK Technique

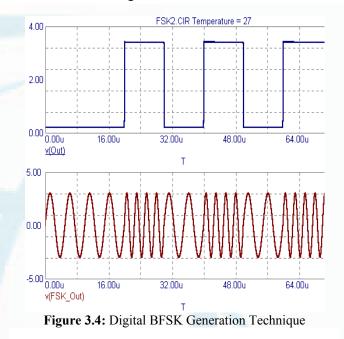

Frequency shift keying (FSK) is the most common form of digital modulation in the high-frequency radio spectrum, and has important applications in telephone circuits. Binary FSK (usually referred to simply as FSK) is a modulation scheme typically used to send digital information between digital equipment such as tele-printers and computers. The data are transmitted by shifting the frequency of a continuous carrier in a binary manner to one or the other of two discrete frequencies. One frequency is designated as the "mark" frequency and the other as the "space" frequency. The mark and space correspond to binary one and zero, respectively. By convention, mark corresponds to the higher radio frequency. Figure 1 shows the relationship between the data

and the transmitted signal. The most commonly used signal parameters for describing an FSK signal are shown in Figure 3.4. The minimum duration of a mark or space condition is called the element length.

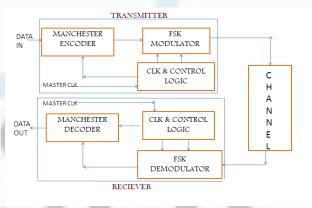

#### 4. Implementation of Telemetry System

In this project both Using Verilog Hardware Description Language (VHDL) both transmitter and receiver sections of telemetry link will be designed. The following block diagram gives a top level view of telemetry link that will be simulated and synthesized. The experimental diagram is shown in Figure 4.1 below.

#### 5. Simulation Results

The software used here is **Verilog.** Verilog, like any other hardware description language, permits a design in either Bottom-up or Top-down methodology. **Verilog** is a great low level language. Structural models are easy to design and Behavioral RTL code is pretty good. The syntax is regular and easy to remember. It is the fastest HDL language to learn and use. However Verilog lacks user defined data types and lacks the interface-object separation of the VHDL's entity-architecture model. Volume 2 Issue 3, March 2014

#### 5.1 Synthesis of Telemetry Transmitter

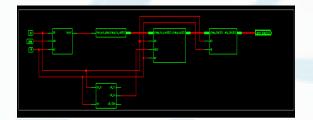

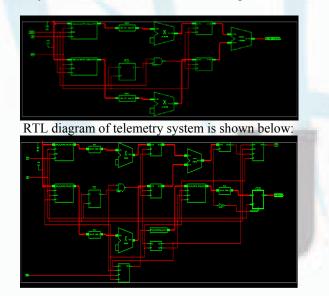

The RTL schematic for telemetry transmitter generated by the Xilinx synthesis tool is shown in the below figure:

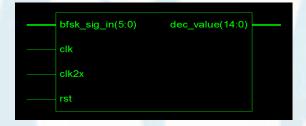

The block diagram showing the ports for telemetry receiver:

The RTL schematic for telemetry receiver generated by the Xilinx synthesis tool is shown in the below figure:

#### 5.2 Transmitter Section:

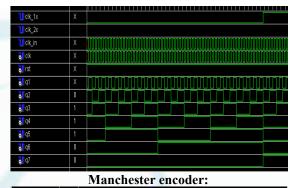

In transmitter section the clock unit shows:

BFSK modulation: BFSK mod controller:

| 🛄 man_enc         | 0     |                                    |                                                                                |

|-------------------|-------|------------------------------------|--------------------------------------------------------------------------------|

| 🗉 📑 phase_in      | 1     | 0103 2 1 2 1                       | $\chi$ 2 $\chi$ 1 $\chi$ 2 $\chi$ 1 $\chi$ 2 $\chi$ 1 $\chi$ 2 $\chi$ 1 $\chi$ |

|                   |       | Phase accumulat                    | or:                                                                            |

| UI clic           |       |                                    |                                                                                |

| Li rst            |       |                                    |                                                                                |

| UI clk2x          | 1     |                                    |                                                                                |

| 🖬 📑 phase_inc_wo  |       |                                    | 2                                                                              |

| phase_out(5:0)    | -     | 48 50 52 54 56 58 60 5             | 62 X 0 X 2 X 4 X 6 X 8 X 10 X                                                  |

| 🖬 💸 phase_inc_re. |       |                                    | 2                                                                              |

| phase_reg_ou      | 15:01 | 48 50 52 54 56 58 60 5             | 62 X 0 X 2 X 4 X 6 X 8 X 10 X                                                  |

| acc_output(5:0)   |       | 50 X 62 X 54 X 66 X 68 X 60 X 62 X | 0 X 2 X 4 X 6 X 8 X 10 X 12 X                                                  |

| 🔊 local_rst       |       |                                    |                                                                                |

| all delayed_clk2x |       |                                    |                                                                                |

**Transmitter Section Output:**

| ol rst             | 1  |                                                            |                       |

|--------------------|----|------------------------------------------------------------|-----------------------|

| olk 🛛              | 0  | , ערע אין              |                       |

| 🏹 data             | 0  |                                                            |                       |

| 🏭 mout             | 0  |                                                            |                       |

| 🔟 clk2x            | 1  |                                                            |                       |

| 11 clk_2x          | 1  |                                                            |                       |

| UI clk_in          | 0  |                                                            | واوارارارارارا        |

| 🗄 🛃 phase_inc_wor  | 1  |                                                            |                       |

| 🗈 🛃 phase_out(5:0) | 0  | <u>104680024280024380044466666666666</u>                   | 0 1/2/3/4/5/6/7       |

| 🗉 🚮 amp_bit(5:0)   | 32 | 11912(6)(0)585249423935( 33 )353942465259(0)(3)(9)15202429 | (32 ) 31 ) 30 29 28 2 |

5.3 Receiver Section:

ŧ

|   |                         |   | Clock unit: |

|---|-------------------------|---|-------------|

| - | 1] clk_1x               | X |             |

| - | <mark>11)</mark> clk_2x |   |             |

|   | <mark>11</mark> clk_in  | Х |             |

|   | <mark>ð∏</mark> clk     | Х |             |

|   | 🚮 rst                   | Х |             |

|   | 👌 q1                    | Х |             |

|   | <mark>ð (</mark> q2     | 0 |             |

|   | <mark>ð 1</mark> q3     | 1 |             |

|   | <mark>ð 1</mark> q4     | 1 |             |

|   | <mark>ð 1</mark> q5     | 1 |             |

|   | <mark>80</mark> q6      | 0 |             |

|   | <b>6</b> ] q7           | 0 |             |

#### **BFSK Demodulation:**

| l 📑 x(1 4:0) | 1 | 10024 | -6304 | 10024 | (•) | (1) | (·) | (1) | (•) | (1) | () | (1) | •) | (1) | (•) | (1) | (•) | 1) | () | 002 |

|--------------|---|-------|-------|-------|-----|-----|-----|-----|-----|-----|----|-----|----|-----|-----|-----|-----|----|----|-----|

| 🚺 out_bits   | 0 |       |       |       |     |     |     |     |     |     |    |     |    |     |     |     |     |    |    |     |

| 🔰 out_bit1   | 0 |       |       |       |     |     |     |     |     |     |    |     |    |     |     |     |     |    |    |     |

## International Journal of Scientific Engineering and Research (IJSER)

www.ijser.in ISSN (Online): 2347-3878

Volume 2 Issue 3, March 2014

|           |   | Manchester Decoding: |

|-----------|---|----------------------|

| 🚺 clk2x   | 1 |                      |

| UI cik1x  | 1 |                      |

| 11 rst    | 1 |                      |

| 🛄 dmi     | 1 |                      |

| 🎝 mdi_buf | 0 |                      |

| omdi_buf2 | 0 |                      |

|          |   | Receiver Section Output: |               |

|----------|---|--------------------------|---------------|

| 1) dout1 | 0 |                          |               |

| 🛄 clk    | 1 |                          |               |

| 🛄 clk2x  | 0 |                          |               |

| 🛄 clk_1x |   |                          |               |

| 🔟 clk_in | 1 |                          | $\mathcal{N}$ |

| 🛄 rst    | 1 |                          |               |

| 🛄 dmi    | 0 |                          |               |

|          |   |                          |               |

#### 5.4 Telemetry System Output:

| 🗉 🛃 amp_bit(5:0)    | 6'h21 |  |

|---------------------|-------|--|

| <mark>Ul</mark> cik | 1     |  |

| 🔟 rst               | 1     |  |

| 🗓 data              | 0     |  |

| 🛄 dout              | 0     |  |

#### 6. Conclusions and Future Scope

The telemetry system is developed to communicate data that identified in the objects characterization or parameters which give a clear idea to analyze the moving objects in real time and space which is an important characterization in day to day life. Designed a telemetry system in VERILOG and successfully simulated it through XILINX. Using digital techniques, an effective link was designed. The digital techniques used in design makes the FSK modulator and demodulator sections to be flexible in modifying the frequencies and other parameters. By the features of XILINX generated successful simulation results can be dumped into FPGA which results a practical telemetry system. By using more advanced techniques, an advanced telemetry system is designed which can be more reliable and accurate in transmission. The telemetry, tracking and command (TT&C) system of a spacecraft provides the most vital telecommunication link between a satellite and ground station. Scope is to design Telemetry system in VERILOG HDL and successfully simulated it in XILINX. This simulated result can be dumped into FPGA further in which results practical telemetry system it to for telecommunication link between satellite and ground station. Advanced telemetry system is designed which is more reliable and accurate in transmission.

## References

- [1] Dr. Frank Carden, Dr. Robert Henry, Dr. Rus Jedlicka. Telemetry System Engineering, Artech House Telecommunications Library

- [2] "Telemetry: Summary of concept and rationale". NASA. NASA Technical Reports Server. Retrieved 26 September 2011.

- [3] Mayo Wells "The Origins of Space Telemetry", Technology and Culture, 1963.

[4] Joachim & Mueller, "Trends in Missile and Space Radio Telemetry"

# **Author Profile**

**Prof. M. Purnachandra Rao** received his M.Sc (Tech) in Electronics from Andhra University 1980 and he was awarded his Ph.D. from Dept. of Physics, Andhra University. Later on appointed has Assistant Professor, Associate Professor and Professor in Physics Department and Head of the Dept. of Systems Design. Has 30 years of experience in the field of SODAR and its applications.

**N. P. Lavanya Kumari** received M. Sc, M. Phil in Electronics and M. Tech degrees in Electronics & Communication Engineering from Andhra University in 2004, 2008 and 2012 respectively. She is working as an Asst. Professor in the Department of Systems Design, A.U. Visakhapatnam.

A. Sarvani received M.Sc. (Tech) in Electronics and Instrumentation and M. Tech degree in Electronics & Communication Engineering from Andhra University in 2008 and 2012 respectively. Presently she is Research Scholar in the Department of Systems Design, A.U. Visakhapatnam.

**K. S. S. Soujanya Kumari** received M. Sc and M. Phil degrees in Electronics from Andhra University in 2004 and 2008. She is working as Teaching Associate in the Department of Systems Design, A.U. Visakhapatnam.

**L. Yamini Swathi** received M. Sc and M. Phil degrees in Electronics from Andhra University in 2004 and 2008. She is working as Teaching Associate in the Department of Systems Design, A.U. Visakhapatnam.